#### KING FHAD UNIVERSITY OF PETROLEUM & MINERALS

Collage of Computer Sciences & Engineering Department of Computer Engineering

# COE305 Microcomputer Systems Design Lab Manual

COE305 LAB MANUAL

## **Microcomputer Systems Design**

by Dr. Abdul Rahim Naseer Mr. Khaled Al-Utaibi

Mr. Hazem Selmi

## **Table of Contents**

#### Design & Fabrication of an 8086 Microprocessor System

| • | Interfacing the Clock Generator to the CPU | 2  |

|---|--------------------------------------------|----|

| • | Designing the Bus System                   | 5  |

| • | Designing the Memory System                | 8  |

| • | Interfacing I/O Ports                      | 12 |

| • | Testing the 80806 Microcomputer System     | 15 |

# Interface Experiments Using 8086 Microprocessor Kits & Application Boards

| • | Flight 8086 Training Board                                    | 21 |

|---|---------------------------------------------------------------|----|

| • | Conducting Simple I/O Operations Using Flight 86 Training Kit | 30 |

| • | Generating Timing Sequences                                   | 37 |

| • | Analog To Digital & Digital To Analog Conversion              | 47 |

| • | Controlling Dc Motors                                         | 54 |

| • | Interfacing A Hyper Terminal To The Flight 86 Kit             | 59 |

Mini Project

#### **Appendices**

#### Part

## Design & Fabrication of an 8086 Microprocessor System

I n this part of the lab, the students are required to design and fabricate an 8086 based microcomputer system. The lab experiments in this part, consist of designing, assembling and testing of the fabricated system. The design, assembling and testing will be carried out by the students in an incremental manner as indicated below.

- **1.** Connecting and testing clock driver circuit with microprocessor.

- 2. Connecting and testing address buffers and data bus drivers with microprocessor

- 3. Connecting and testing memory and I/O decoders

- **4.** Connecting and testing memory devices (EPROMs, RAMs) with the processor

- **5.** Connecting and testing I/O ports.

- 6. Writing assembly language programs for simple applications.

# **Interfacing the Clock Generator to the CPU**

#### **1.1 Background**

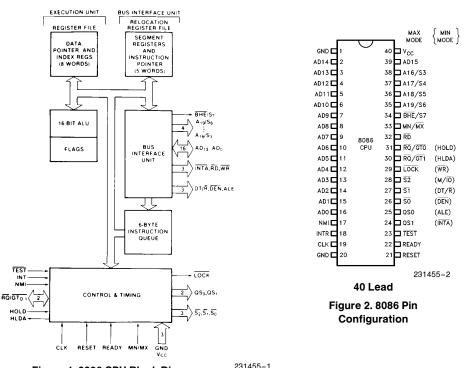

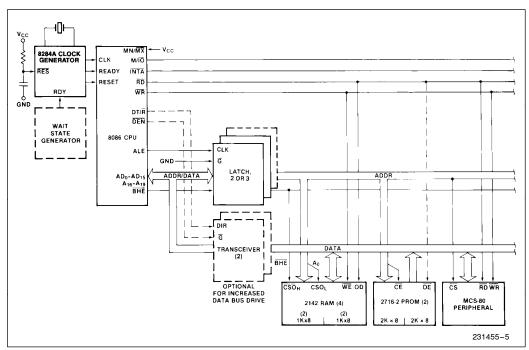

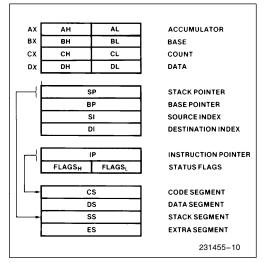

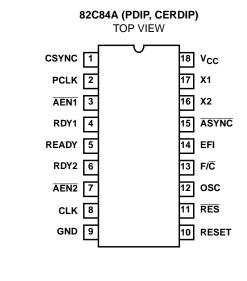

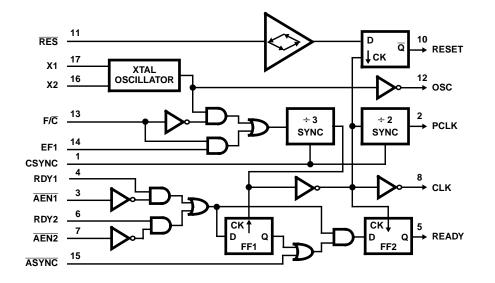

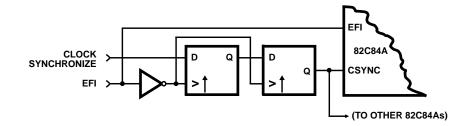

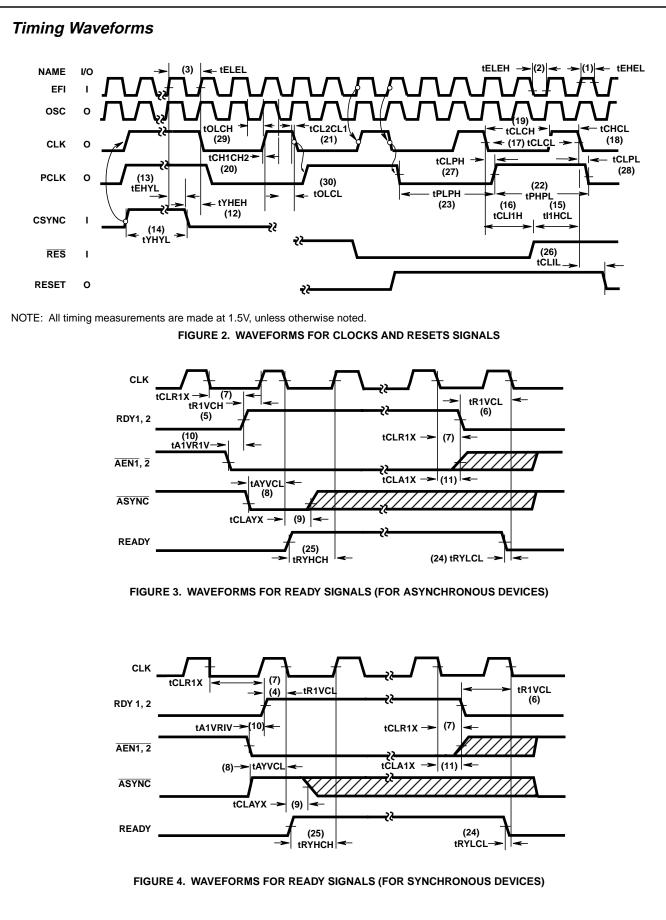

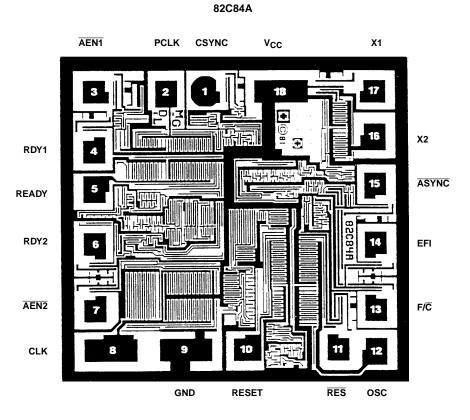

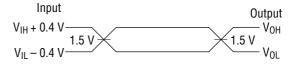

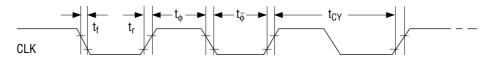

The 8086 CPU has 16 data lines and 20 address lines. The CPU uses time multiplexing for the Address, data, and some status lines. The Clock Generator and Driver 8284 is a device capable of providing the CPU with Clock, reset logic, and ready logic. For this it uses a crystal oscillator that must be 3 times the frequency of the CPU (15 MHz Crystal).

#### **1.2 Objective**

Interfacing the clock generator to the CPU

#### **1.3 Equipment**

The instructor should group the students (2 or 3 per group) and assign a group head. The group head will take the following equipment on his responsibility as a loan from COE department. From now on, in every experiment there will be more equipment given. The group will keep the equipment and use them through the following experiments. They should return every thing before reporting the grades.

- Proto board,

- 8086 CPU,

- 8284 Clock generator,

- 15 MHz crystal clock,

- 1 Reset-Switch,

- 3 resistors (100K, 510, 510),

- 1 Capacitor (10u), and

- Oscilloscope

#### **1.4 Procedure**

**1.** Make a short review of the clock generator 8284 (Appendix II) and identify the three major functions that this device can operate.

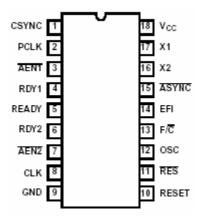

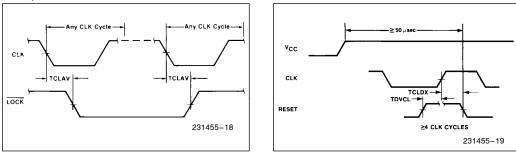

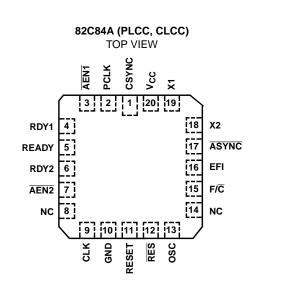

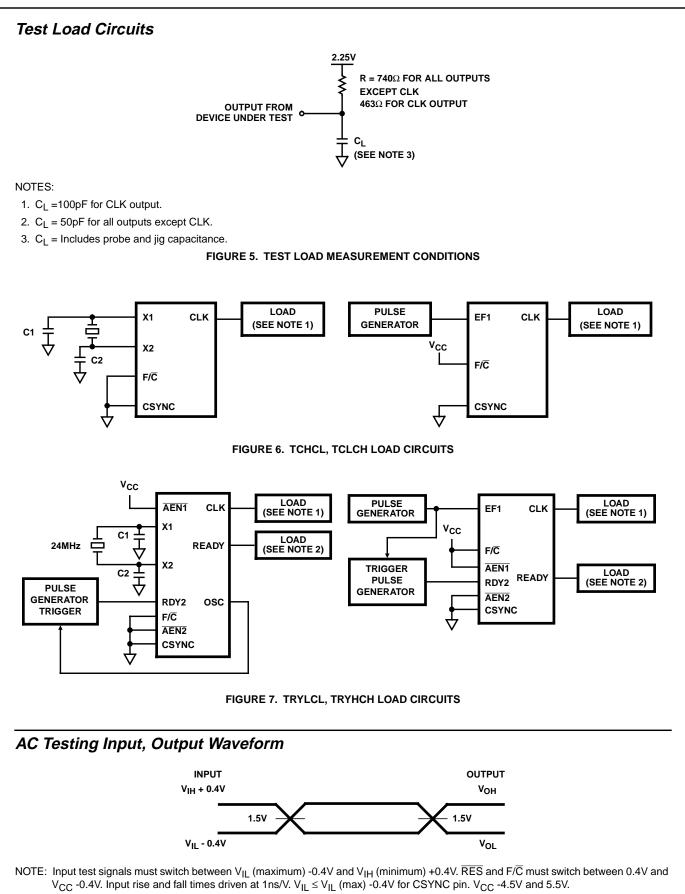

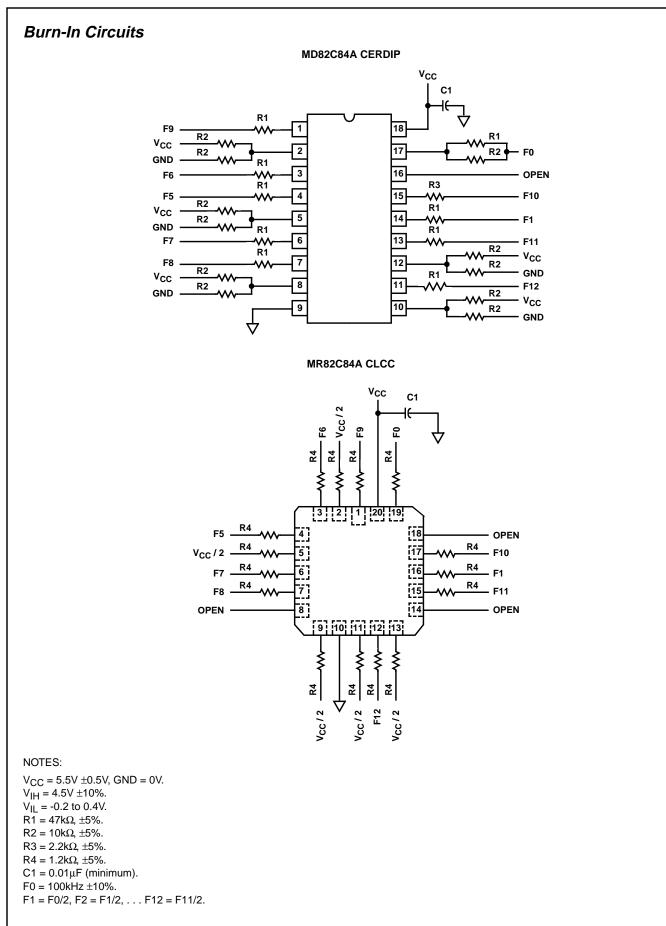

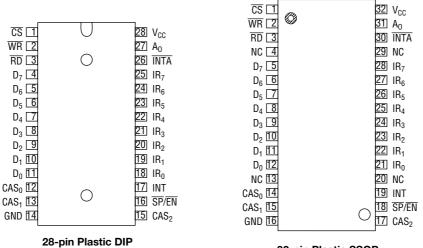

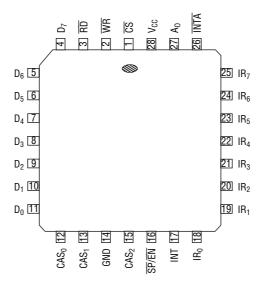

Figure 1.1: Top view of the 8284 clock generator

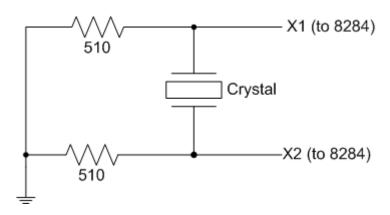

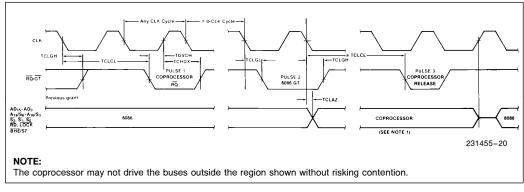

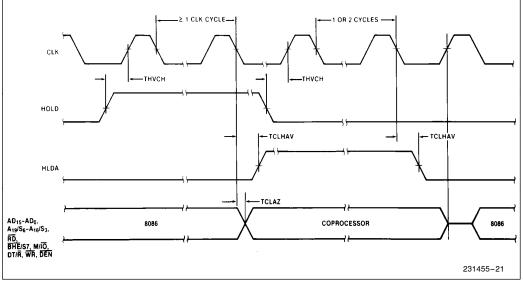

**2.** Implement the design shown in Figure 1.2 and check the output signal at CLK, PCLK, and OSC using the oscilloscope. Interface the CLK line to CPU and show your instructor the resulting signals.

Figure 1.2:Connecting the crystal to the 8284

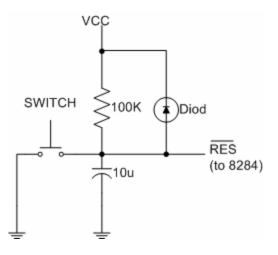

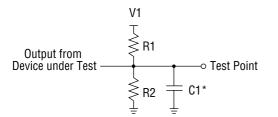

**3.** Implement the RESET circuit shown in Figure 1.3, and make sure that any change from 0 to 1 must have duration of at least 50us. Test the reset signal using the oscilloscope and show the resulting signal to your instructor.

Figure 1.3: Reset Circuit

**4.** Read pin description of the 8086 microprocessor (Appendix), and determine what should be connected to the following pins (assume minimum mode):

| a. | $MN / \overline{MX}$ | (pin 33) |

|----|----------------------|----------|

| b. | HOLD                 | (pin 31) |

| c. | TEST                 | (pin 23) |

| d. | READY                | (pin 22) |

| e. | RESET                | (pin 21) |

| f. | CLK                  | (pin 19) |

| g. | INTR                 | (pin 18) |

| h. | NMI                  | (pin 17) |

|    |                      |          |

**5.** Connect VCC and GND pins of the 8086 microprocessor and test the ALE signal (pin 25) using the oscilloscope.

#### **Exercises**

- **1.1.** What is the relationship between frequencies on the lines CLK, PCLK, and OSC? Do these frequencies match with the description of the 8284?

- **1.2.** Find out the proper values of the needed resistors and capacitors in the RESET circuit such that any change from 0 to 1 must ensure duration of 50us.

- **1.3.** What is the function of the ready signals on the 8284?

### **Designing the Bus System**

#### 2.1 Background

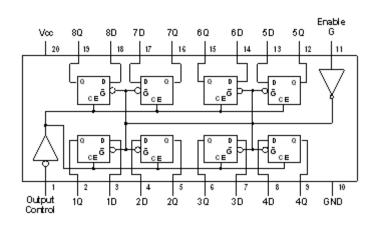

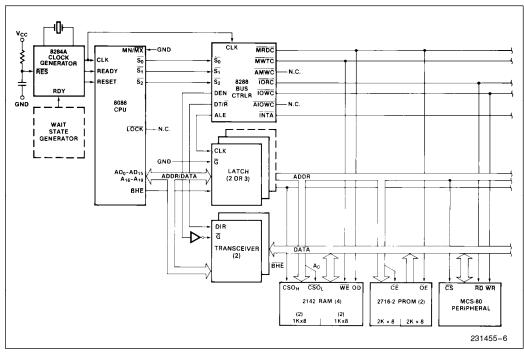

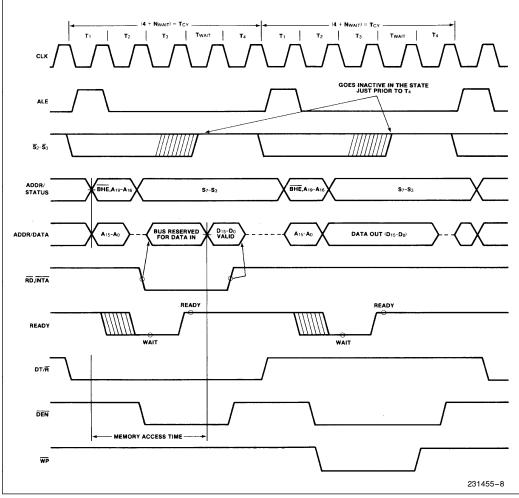

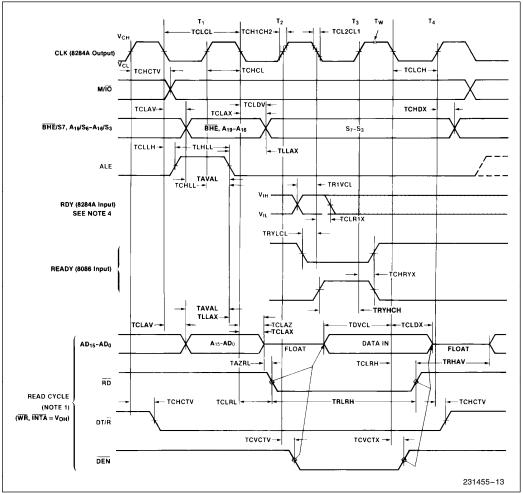

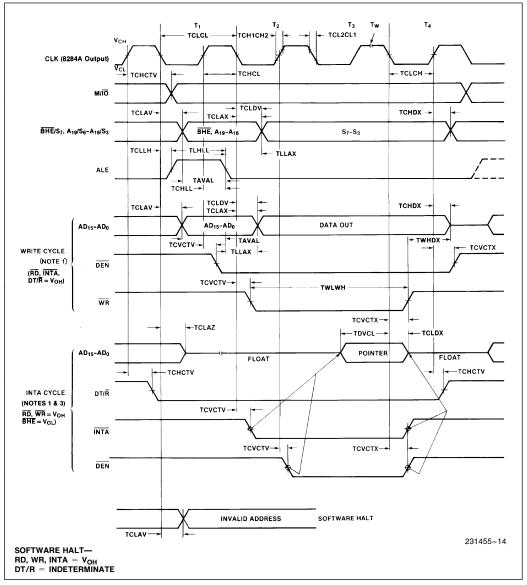

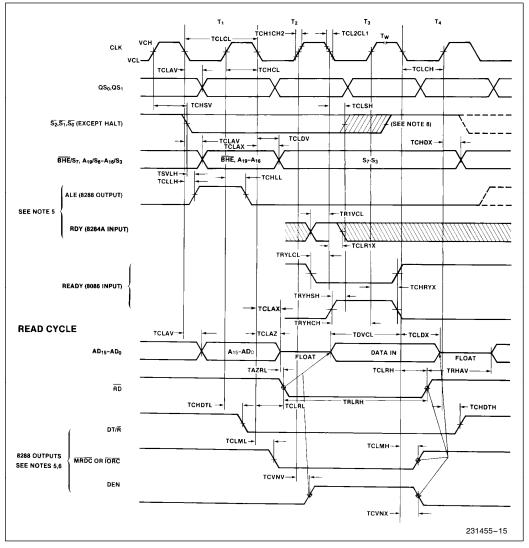

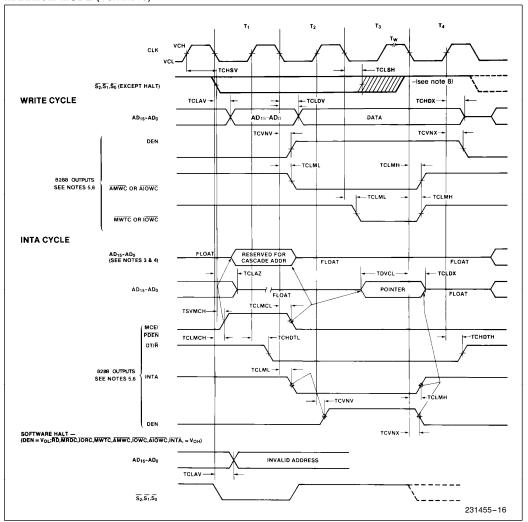

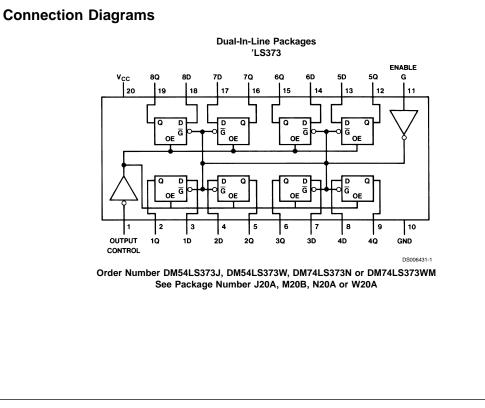

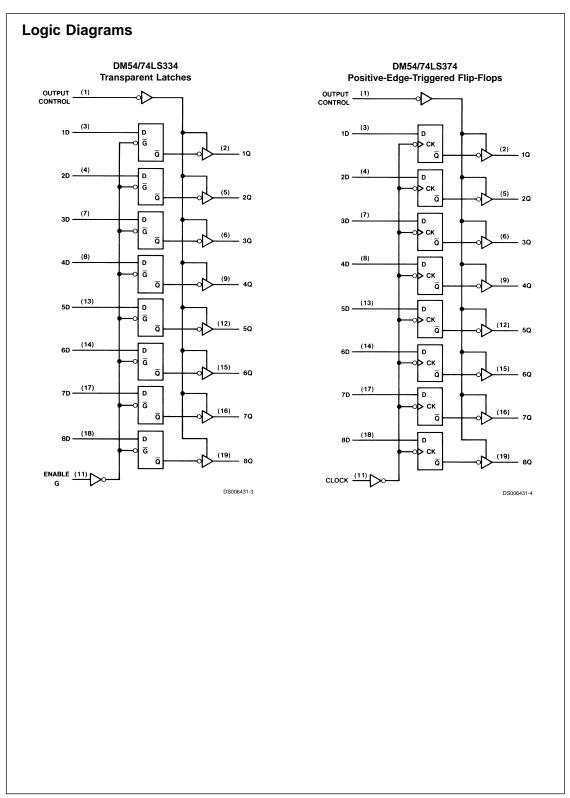

The 8086 CPU has 16 data lines and 20 address lines. The CPU uses time multiplexing for the address, data, and some status lines. The CPU generates the addresses A0-A15 on lines AD0- AD15 and A16-A19 on lines AS16-AS19 during clock T1. This event is indicated by a bus control signal ALE. During T2, T3, and T4 the CPU uses the AD0- AD15 to transfer data, i.e. as data bus. Demultiplexing of the AD lines requires latching of the addresses by using some integrated latches (e.g. 74LS373 octal latches). The latched addresses will then be used as address bus during clocks T2, T3, and T4.

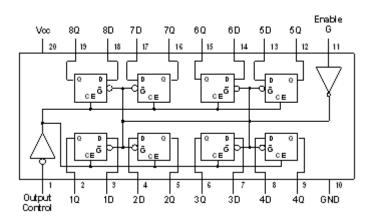

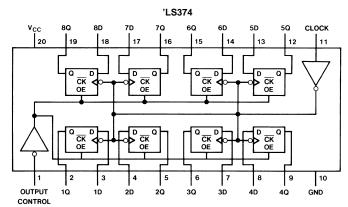

The 74LS373 octal latch is a simple level-triggered D flip-flops with two control lines: *Output Control* (OC) and *Latch Enable* (G). As long as the Latch Enable (G) is high, the outputs of the D flip-flops follow their inputs. When G goes low, the flip-flops latch (save) the input signals. The output control line (OC) can be used to place the eight latches in either a normal logic state (high or low logic levels), or a high-impedance state.

#### 2.2 Objective

To provide a demultiplexed data and address buses for the 8086 CPU through the use of the 74LS373 octal latches

#### 2.3 Equipment

- The prototype-board that already includes an 8086 microprocessor with clock generator,

- TTL 74LS373 octal latches, and

- Multimeter

#### 2.4 Procedure

- **1.** Review the function of the 74LS373 octal latch (Appendix). Identify its input and output lines as well as the control signals available on this chip.

- **2.** Each group discuss and give solutions to the following issues:

- a. What are the AD and AS lines that must be demultiplexed?

- b. The number of needed octal latches.

- c. What should be connected to control lines of the 74LS373 octal latch (i.e. G and OC).

- **3.** Each group present their design of the demultiplexed bus to the lab instructor for validation. The proposed design must be completely defined on a working map, and the same map must be used in the wiring and debugging. The design must show what should be connected to the Latch Enable (G) and Output Control (OC) lines.

- **4.** Once the design is validated, the group can start wiring based on the working map.

- **5.** After completing the wiring, each group must carry out visual and electrical testing of the connections (e.g. using multimeters) as well as doing necessary corrections.

## Designing the Memory System

#### 3.1 Background

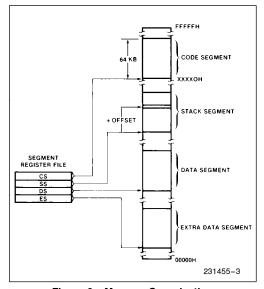

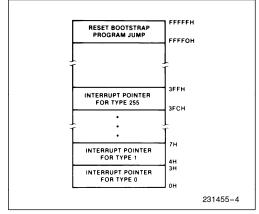

The 8086 CPU has addressing capability of 1 Mega Bytes as well as a 16-bit data bus. Basically, EPROM and SRAM memory chips are byte organized. The 8086 CPU requires that the memory be organized as two banks called the even and odd banks. The EPROM memory is to store resident programs that must run when the microprocessor system is powered on. The SRAM memory is used to store application programs that are ready to run as well as to provide some reserved locations for the proper operations of interrupts. The designer must be careful with bank selection especially when dealing with read/write memories. In this case, byte operations with one bank must be done while enabling one of the memory banks and disabling the other. This experiment should expose the student to a number of issues such as:

- 1. Partitioning of the memory address space,

- 2. Distinguishing between addressing capability and physical memory,

- **3.** Dealing with partial and exhaustive addressing, arid

- **4.** Studying address decoding techniques

#### 3.2 Objective

Designing and implementing a small memory system using SRAM and EPROM memory chips

#### 3.3 Equipment

• The prototype-board that already includes an 8086 CPU operating in minimum mode with clock generator and a fully demultiplexed data and address buses,

- Two 8 Kbytes SRAM memories (6264), and

- Two 8 Kbytes EPROM memories (2764)

#### 3.4 Procedure

In this project, each group will design a memory system consisting of two memory modules. The first is a 16 KByte SRAM starting at address 00000h. The second is a 16 KByte EPROM ending at address FFFFh (Why?). Refer to your text book for more details about memory system design.

- **1.** Each group discuss and answer the following issues:

- a. What is the number of address lines required to address the two modules?

- b. How to design the 32 KBytes memory system using partial decoding?

- c. How to design the same memory system using exhaustive (full) decoding?

- d. What address lines to be connected to the even and odd banks of the two modules?

- e. How to distinguish the even and odd banks of the SRAM module?

- f. Is it necessary to distinguish the even and odd banks of the EPROM module? Why?

- 2. Design the above memory system by using two 8 KBytes SRAM memories (6264) and two 8 KBytes EPROM memories (2764). Show your design to the lab instructor and implement it after validation. Your design should show, for each memory chip, what should be connected to:

- a. Address and data pins

- b. Chip select  $(\overline{CS})$

- c. Output Enable (OE)

- d. Write Enable (WE)

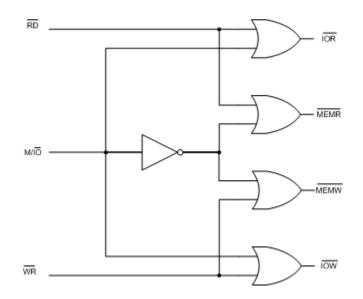

- Implement the decoder shown in Figure 3.1 which takes as input RD,

WR and M / IO, and produces memory read (MEMR), memory write (MEMW), I/O read (IOR) and I/O write (IOW) signals.

- **4.** After completing the wiring, each group must carry out visual and electrical testing of the connections (e.g. using multimeters) as well as doing necessary corrections.

Figure 3.1: Generating the four memory and I/O control bus signals from the 8086's RD, WR and I/O signals.

| 7264   |     |    |       |  |  |  |  |  |  |  |

|--------|-----|----|-------|--|--|--|--|--|--|--|

| NC 🗆   | 1 C | 28 |       |  |  |  |  |  |  |  |

| A12 🗖  | 2   | 27 | PGM   |  |  |  |  |  |  |  |

| A7 🗆   | 3   | 26 | Ы ИС  |  |  |  |  |  |  |  |

| A6 🗆   | 4   | 25 | D A8  |  |  |  |  |  |  |  |

| A5 🗆   | 5   | 24 | EA 🛛  |  |  |  |  |  |  |  |

| A4 🗆   | 6   | 23 | A11   |  |  |  |  |  |  |  |

| A3 🗆   | 7   | 22 | ⊨ œ   |  |  |  |  |  |  |  |

| A2 🗆   | 8   | 21 | A10   |  |  |  |  |  |  |  |

| A1 🗆   | 9   | 20 | D CE  |  |  |  |  |  |  |  |

| A0 🗆   | 10  | 19 | 107   |  |  |  |  |  |  |  |

| 100 🗆  | 11  | 18 | 106   |  |  |  |  |  |  |  |

| 101 🗆  | 12  | 17 | 105   |  |  |  |  |  |  |  |

| 102 🗆  | 13  | 16 | 104   |  |  |  |  |  |  |  |

| GND    | 14  | 15 | D 103 |  |  |  |  |  |  |  |

| 8K × 8 |     |    |       |  |  |  |  |  |  |  |

|        | EPR | ОМ | EPROM |  |  |  |  |  |  |  |

28 🛛 VCC

27 🕇 WE

26 🗋 NC

25 🗋 A8

24 🗋 A9 23 🗋 A11

22 🗋 😇

21 🗋 A10

20 🗋 🖻

19 🗋 107

18 106

17 105 16 🗋 104

15 🗋 103

|          | 6264    |       |                                          | 626  | 4   |

|----------|---------|-------|------------------------------------------|------|-----|

|          |         | 1     | r                                        |      |     |

| NC 🗖 1   | 0 28    |       |                                          | 1 0  | 2   |

| A12 🗖 2  | 27      |       | A12 🗖                                    | 2    | 2   |

| A7 🗖 3   | 26      |       | A7 🗖                                     | 3    | 2   |

| A6 🗖 4   | 25      |       | A6 🗆                                     | 4    | 2   |

| A5 🗌 5   | 24      | □ A9  | A5 🗌                                     | 5    | 2   |

| A4 🗆 6   | 23      | D A11 | A4 🗆                                     | 6    | 2   |

| A3 🗖 7   | 22      | 卢ᅙᄐ   | A3 🗆                                     | 7    | 2   |

| A2 🗌 8   | 21      | A10   | A2 🗖                                     | 8    | 2   |

| A1 🗌 9   | 20      | 는 CE  | A1 🗖                                     | 9    | 2   |

| A0 🗌 10  | 19      | D 107 | A0 🗖                                     | 10   | 1   |

| 100 🗖 11 | 18      | D 106 | 100 🗆                                    | 11   | 1   |

| 101 🗖 12 | 2 17    | 105   | 101 🗖                                    | 12   | 1   |

| 102 🗖 13 | 16      | 104   | 102 🗆                                    | 13   | 1   |

| GND 14   | 15      | D 103 | GND                                      | 14   | 1   |

|          | 8K × 8  | 1     | L. L | 8K × | 8   |

|          | SRAM    |       |                                          | SRA  |     |

|          | OT VAIN |       |                                          | UNA  | 141 |

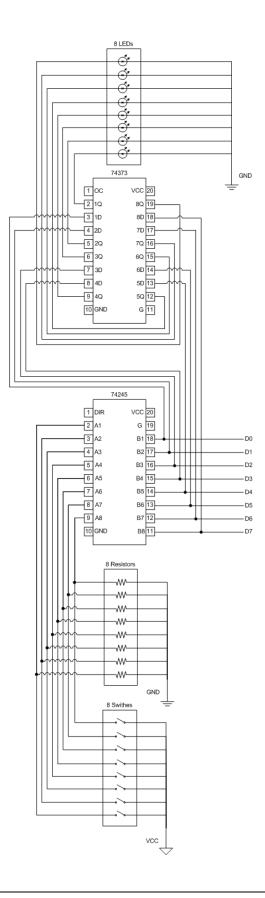

### **Interfacing I/O Ports**

#### 4.1 Background

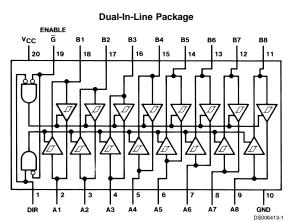

The I/O ports are very essential in any computer system because they enable the user to communicate with the system. In this experiment, we will design and implement a very simple form of I/O ports (switches for input and LEDs for output).

The input port should be designed to pass the data on the input switches to the data bus if and only if an *input instruction* (I/O read cycle) is executed by the CPU. This can be achieved using a tri-state buffer that will be enabled only during I/O read cycles.

The output port should be capable of storing the data on the bus when the CPU performs an *output instruction* (I/O write cycle). In this case, a latch can be used to store the output data and supply it continuously to the LEDs. The latch should be enabled to pass its input to the LEDs only when the CPU is writing to the output port (i.e. I/O write cycle).

Just as each memory location has its own (memory) address, each I/O port has its own (port) address. However, since we are using only one input port and one output port, we will not assign any addresses to our I/O port. Thus, I/O instructions can use dummy addresses to access our I/O ports.

#### 4.2 Objective

Interfacing simple I/O ports the 8086 microcomputer system

#### 4.3 Equipment

- Use of a prototype-board that already includes an 8086 CPU operating in minimum mode with clock generator and a fully demultiplexed data and address buses in addition to two 8 Kbytes SRAM memories (6264) and two 8 Kbytes EPROM memories (2764),

- TTL 74LS245 tri-state buffer,

- TTL 74LS373 octal latch,

- 8 Switches,

- 8 LEDs, and

- 8 resisters

#### 4.4 Procedure

- **1.** The lab instructor should explain how to connect the switches and LEDs to the system

- **2.** Each group should draw a complete circuit diagram of the input port using 74LS245 that shows what should be connected to its inputs, outputs and control lines.

- **3.** Each group should draw a complete circuit diagram of the output port using 74LS373 that shows what should be connected to its inputs, outputs and control lines.

- 4. Confirm your design with the lab instructor then start wiring

14

# 5

# **Testing the 80806 Microcomputer System**

#### 5.1 Introduction

By this experiment your system should include the following:

- 1. an 8086 microprocessor,

- 2. a clock generator with 15MHz crystal,

- **3.** a fully demultiplexed bus system (74LS373 octal latches),

- **4.** a memory system including two SRAM memory chips and two EPROM memory chips each of size 8Kbytes,

- 5. decoders, and

- 6. simple I/O ports (switches, LEDs, tri-state buffer, and octal latch)

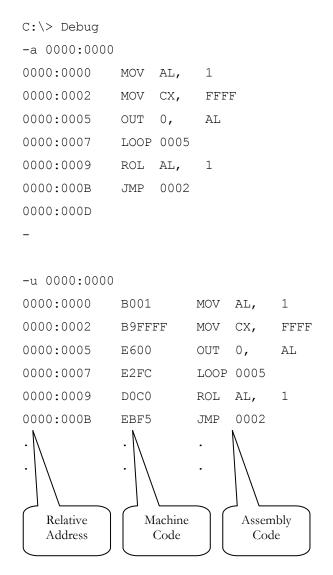

To find if the system is working properly, we will write a simple program (see Figure 5.1) that light LEDs one after another one at a time in a sequence from right to left.

|     | MOV  | AL,  | 01h           | ;set the LSB of register AL              |

|-----|------|------|---------------|------------------------------------------|

| L1: | MOV  | CX,  | <b>OFFFFh</b> | ;load the counter CX with FFFFh          |

| L2: | OUT  | 00h, | AL            | ;output AL to port 00h (output port)     |

|     | LOOP | L2   |               | ;repeat the operation until CX becomes 0 |

|     | ROL  | AL,  | 1             | ;rotate AL one bit position to the left  |

|     | JMP  | L1   |               | ;go back to Ll                           |

Figure 5.1: Test Program

#### 5.2 Equipment

- Use of a prototype-board that already includes an 8086 CPU operating in minimum mode with clock generator and a fully demultiplexed data and address buses in addition to two 8 Kbytes SRAM memories (6264) and two 8 Kbytes EPROM memories (2764),

- MS-DOS Debugger,

- EPROM Eraser,

- EPROM Programmer,

- Oscilloscope,

- Logic Probe, and

- Multimeter

#### 5.3 Procedure

- **1.** Use the MS-DOS debugger to find the machine code of the test program as shown in Figure 5.2.

- **2.** Take out the EPROMs from your system and label them as EVEN BANK and ODD BANK.

- **3.** Place the two chips in the EPROM eraser.

- **4.** Load the machine code of the test program (see Figure 5.3) into the EPROMs using the EPROM programmer (Load even bytes of the machine code into the even back, and the odd bytes into the odd bank).

- **5.** Place the programmed EPROMs back on your prototype-board.

- **6.** Make sure that the EVEN BANK chip is connected to the even byte of the bus (D0-D7) and the ODD BANK chip is connected the odd byte of the bus (D8-D15).

- **7.** Connect your system to the power supply and check output displayed on the LEDs.

COE305 LAB MANUAL

Figure 5.2: Finding the machine code

| Byte #       | 0          | 1  | 2  | 3  | 4  | 5  | 6  | 7  | 8  | 9  | 10 | 11 | 12 | 13 |

|--------------|------------|----|----|----|----|----|----|----|----|----|----|----|----|----|

| Machine Code | <b>B</b> 0 | 01 | B9 | FF | FF | E6 | 00 | E2 | FC | D0 | C0 | EB | F5 | FF |

Figure 5.3: Machine code to be loaded into the EPROMs

#### 5.4 Debugging the System

In case that your system is not functioning, you can carry out hardware testing of the microcomputer system through general inspection and hardware debugging as explained in the following steps:

Step 1: Visual inspection and testing:

- **1.** Make sure that the VCC and GND you are using are appropriate. Use oscilloscope to measure VCC on your system.

- **2.** Identify the VCC and GND lines on your board and make sure all chips receive them on the right pins. For this you may carry out visual inspection to avoid applying reverse voltage on the chips.

- **3.** Test all VCC and GND on all the chips using the Oscilloscope or a Logic Probe.

- **4.** Check the following signals using the Oscilloscope:

- a. the Reset circuit at the input of 8086 CPU,

- b. the CLK input of 8086 CPU, and

- c. the ALE output of 8086 CPU.

- **5.** Using a multimeter and the map of your design you need to check the following:

- a. all inter-connections between the address bus lines at output of octal latches and the memories,

- b. all inter-connections between the CPU and memories data lines, and

- c. all control connections for Read/Write, chip-select, and <u>all default</u> <u>connections</u>.

Step 2: Testing the logic operations of the system.

We expect the test program (Figure 5.1) to generate some pattern of chip select on the EPROM memory because the program is stored there. Also this program is supposed to write data to the I/O port, so we expect I/O write cycles on the control of output port. One may consider that the system is working fine if the chip-select pattern and

I/O write cycles are observed in the right order. For this test we have to follow the steps below:

- **1.** Analyze the program and find out the expected chip-select pattern on the EPROM and I/O write cycles.

- **2.** Turn on your microprocessor system, and use the oscilloscope to check memory and I/O read signals (i.e., chip-select of the EPROMs and latch-enable of the I/O port).

- **3.** If you do not see the expected pattern, then there is still a problem with your system. In this case you need to do further investigation of the system:

- a. Check Reset, CLK, and ALE on the CPU. If an error is found, then correct it and repeat the test.

- b. Check the ALE signal on the control of the octal latches.

- c. You may need to use the Logic Analyzer and set the triggering condition to valid EPROM select, and then follow up the timing step-by-step. Following a reset the CPU must generate the bootstrap address. If it does not, then the starting conditions are not OK. You better carefully check Reset, CLK, and ALE on the CPU. If the above address is generated but control is lost, then your address connections and data connections from CPU to memories are likely to contain some errors. You need to check them again and restart the procedure.

#### **Exercises**

- **5.1.** Write an assembly program that continuously reads one byte from the input port, complement it and sent it to the output port. Test this program on your system.

- **5.2.** Write an assembly program to display an 8-bit counter on the LEDs of your system.

- **5.3.** Write an assembly program to add 2 four-bit numbers and display the result on the LEDs of your system. The two numbers are entered through the 8-DIP switch (i.e. each 4 switches represent one number).

#### Part

# 2

# Interface Experiments using 8086 Microprocessor Kits & Application Boards

In this part, students will be carrying out interfacing experiments using 8086 microprocessor kits and interfacing boards. These kits need to be interfaced to the PCs for downloading programs. In this part, students will get an opportunity to use professionally designed microprocessor system kits and application boards which would enable them to gain enough knowledge and experience in interfacing external circuits to microprocessors for performing different applications.

The lab experiments in this part consist of the following :

- **1.** Studying the microprocessor kit capabilities and interfacing to PC (in order to familiarize with the kit commands for entering, assembling, debugging and running the programs using the kit).

- 2. Conducting the Interfacing experiments using application boards interfaced to the kits. The interface experiments include configuring and programming the peripheral chips 8253(PIT Programmable Interval Timer), 8255(PPI Programmable Peripheral Interface), 8251(PCI Programmable Communication Interface), 8259(PIC-Priority Interrupt Controller) for different applications. The application boards provided with the microprocessor kits are designed to teach a wide variety of control experiments. Circuits provided in the application board include: digital switches, temperature sensor, optical speed/position sensor, light sensor, potentiometer, A/D and D/A converter, DC motor, LEDs, bargraph, and heater.

### Flight 8086 Training Board

#### **Objective**

The aim of this lab experiment is to familiarize the students with Flight 8086 training board.

#### Equipment

Flight 8086 training board, PC with Flight86 software, download cable.

#### **Tasks to be Performed**

- Connecting the 8086 training board to PC (using COM1 port)

- Study of different commands provided by the training board

- Program Entry, Execution and Debugging

- Assembling and disassembling of a program

- Displaying the contents of registers and memory locations

- Modifying the registers and memory contents

- Single-step execution and Breakpoint insertion

- Downloading & uploading a program file.

- Running simple programs to perform

- **1.** Arithmetic operations

- **2.** Finding the smallest/largest number from a given list of numbers

- **3.** Searching for a given number in a list of numbers.

#### 1.1 Background

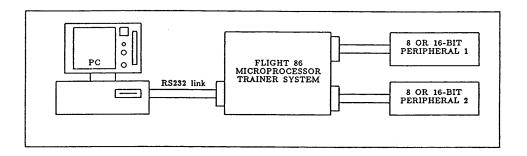

The FLIGHT 86 Trainer System is designed to simplify the teaching of the 8086 CPU and some of its commonly used peripherals. It can be linked to most PCs with a simple serial line, so that code may be assembled and debugged in a supportive software environment before being downloaded into the RAM on the board. The board itself may then be linked to other peripheral devices. A block diagram of this mode of operation is shown in Figure 1.1.

Figure 1.1: Block Diagram of the FLIGHT-86 Trainer System

Once downloaded, the code may be executed and examined in a system which is accessible to the user. Data may be manipulated on the board and the effects viewed on the PC. The software which handles this two-way transfer is supplied with the board, in the form of a monitor program resident on the board in EPROM, and a disk containing the "host" software for the PC.

#### **1.2 Connecting the Training Board to PC**

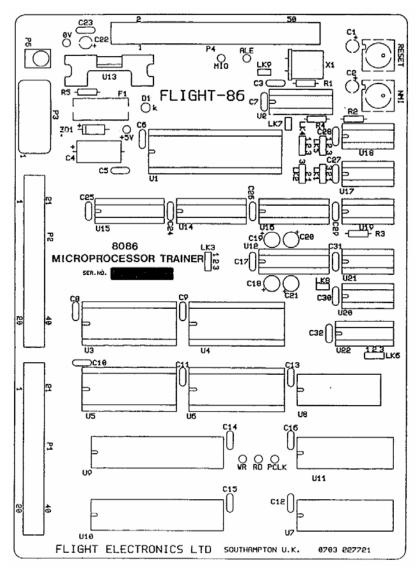

Figure 1.2 shows the FLIGHT-86 Trainer Board layout. The first step is to connect the *serial socket* (P3) on the training board to COM1 in the PC using RS323 cable. Next, connect the power cable to the *power supply connector* (P6). Finally, load the program F86GO.BAT on the PC. This should run and report the amount of RAM and EPROM on the FLIGHT-86 board, before returning the prompt as shown in Figure1.3.

#### **1.3 Commands Provided by Flight-86**

A '-' prompt on the screen means that the host is ready to accept a command. Table1.1 gives a summary of the commands that will be used during this experiment.

Figure 1.2: Layout of the FLIGHT-86 Training Board

```

Loading FLIGHT86 host program, please wait...

FLIGHT86 Controller Board, Host Program Version 2.1

Press ? and Enter for help - waiting for controller board response...

ROM found at F000:C000 to F000:FFFF Flight Monitor ROM version 2.0

RAM found at 0000:0000 to 0000:FFFF

-

```

Figure 1.3: Starting Message of the FLIGHT-86 Training Board

| KEY | PARAMETER                            | DESCRIPTION                                                                             |

|-----|--------------------------------------|-----------------------------------------------------------------------------------------|

| ESC |                                      | Press the Escape button to stop the current command                                     |

| Х   |                                      | Resets the training board                                                               |

| Q   |                                      | Terminates running of the board software<br>and returns control to the operating system |

| ?   | [command letter]                     | Help                                                                                    |

| R   | [register]                           | Allows the user to display or change the content of a register                          |

| М   | [W][segment:] address1 [address2]    | Allows the user to display or change one or<br>more memory locations                    |

| А   | [[segment:] address]                 | Allows the user to write 8086 assembly code directly into the training board            |

| Z   | [[V] [segment:] address1 [address2]] |                                                                                         |

| G   | [[segment:] address]                 | Allows the user to execute code that has<br>been downloaded into RAM                    |

| В   | ?   R   S [segment:] address         | Allows the user to Display/Clear/Set break points inside his code                       |

| S   | [R][[segment:] address]              | Allows the user to step through code one instruction at a time                          |

| :   | [drive:\path] filename               | Loads an Extended Intel Hex file from disk<br>into the memory of the training board     |

Table 1.1: Summary of some commands provided by FLIGHT-86

#### **1.4 The First Program**

#### Assembling a Program (Command A)

The assemble command (A [*segment*:] *address*) allows you to type in 8086 assembly code, and this code will be assembled and stored into the board memory. The following example shows you how to write a simple program using this command

**Example 1.1:** Using the assemble command, write a program that will add the content of two memory locations (words) and store the result in a third memory location.

- 1. Start the line assembler at the desired address by entering **A 0050:0100** (Note that the origin address for user RAM on the FLIGHT-86 is 0050:0100)

- 2. The FLIGHT-86 responds by echoing the address **0050:0100**

#### COE305 LAB MANUAL

- 3. Now enter the assembly code one instruction at a time hitting ENTER after each instruction

- 4. Each time, the FLIGHT-86 responds by echoing the next address

- 5. When you are done exit from the line assembler by pressing ESC button

The screen will now look like

```

A 0050:0100

0050:0100 DW 0002

0050:0102 DW 0003

0050:0104 DW 0000

0050:0106 MOV AX,[0100]

0050:0109 ADD AX,[0102]

0050:010D MOV [0104], AX

0050:0111 INT 5

0050:0113

```

#### **Disassembling a Program (Command Z)**

You can examine what you have entered using the disassemble command. If you type **Z 0050:0100 0111**, then the content of the memory locations between the addresses 0050:0100 and 0050:0111 will be disassembled as follows:

| 0050:0100 | 02 | 00 |    |    | ADD A | AL,  | [вх+ | SI] |

|-----------|----|----|----|----|-------|------|------|-----|

| 0050:0102 | 03 | 00 |    |    | ADD A | AX,  | [BX+ | SI] |

| 0050:0104 | 00 | 00 |    |    | ADD   | [BX+ | sı], | AL  |

| 0050:0106 | A1 | 01 | 00 |    | MOV A | AX,[ | 0100 | ]   |

| 0050:0109 | 03 | 06 | 02 | 01 | ADD A | AX,[ | 0102 | ]   |

| 0050:010D | 89 | 06 | 04 | 01 | MOV   | [010 | 4],  | AX  |

| 0050:0111 | CD | 05 |    |    | INT ! | 5    |      |     |

The HEX numbers between the addresses and the instructions represent the opcodes of the disassembled instructions. Notice that memory words entered as DW directives have been disassembled as ADD instructions with different parameters. This because the values of these memory words are equivalent to the opcode of the ADD instruction with the shown parameters.

#### **Running a Program (Command G)**

To run the above program enter **G 0050:0100** and press the ENTER key. The program will now run, load the word at address 0050:0100 into AX, add the content of the word at address 0050:0102 to the content of AX, store the result into the word at address 0050:0104, and terminate. Note that the instruction **INT 5** is responsible for terminating the program.

#### **Displaying/Modifying Memory Locations (Command M)**

To test the result of the above program enter **M W 0050:0104** and press the Enter key. This will display the memory word at address 0050:0104 where the result of the above program is stored. Exit from this command by pressing the ESC key.

Lets now change the content of the memory words stored at addresses 0050:0100 and 0050:0102. At the command prompt '-', enter M W 0050:0100 and press the Enter key. The content of the memory word at address 0050:0100 is displayed. To change the content of this memory location, enter a HEX number (say 0005) and press the Enter key. The content of the next memory location is displayed. Enter another HEX number (say 0007) and press the Enter key. When the content of the next memory location is displayed, press the ESC key to go back to the command prompt. These steps are shown below:

```

-M W 0050:0100

0050:0100 0002 0005

0050:0102 0003 0007

0050:0104 0005

-

```

Now run the program again and test the content of the memory word at address 0050:0104.

#### **Breakpoint Insertion (Command B)**

This command is intended for debugging user code. A breakpoint is an **INT 3** instruction inserted at an opcode position. The original opcode at this address is saved. When the code is executed it runs normally, at full speed, until it reaches this location. Then, original opcode is restored and the registers, address and first opcode byte are displayed. The user may set another break point and continue with a G instruction.

As an example, enter the command **B S 0050:010D** and press the Enter key. This will set a breakpoint at address 0050:010D in the previous program (i.e. a breakpoint is set at the instruction MOV [0104], AX). Now, run the program using the command **G 0050:0100**. Notice that the program terminates and the message "Monitor breakpoint at 0050:010D" is displayed. This means that the execution of the program using the command **G** location 0050:010D. You can resume the execution of the program using the command **G**, but let us first modify the content of register AX. At the command prompt '-', enter the command **R AX** and press the Enter key. This will display the content of AX which is 000D (i.e. 0005+0007). Modify this value by entering 0001 next to 000D and press the Enter key then ESC to go back to the command prompt. Now, continue the execution of the program from address 0050:010D using the command **G 0050:010D**. Check the content of memory word at address 0050:0104.

COE305 LAB MANUAL

The previous steps are shown below:

```

-B S 0050:010D

-G 0050:0100

Monitor Breakpoint at 0050:010D

-R AX

AX 000C 0001

BX 0000

-G 0050:010D

User Break at 0050:0111

-M W 0050:0104

0050:0104 0001

0050:0106 00A1

-

```

#### **Single-Step Execution (Command S)**

This command is provided to allow the user to step through code one instruction at a time for debugging purposes. The display will be the next instruction address and opcode byte with, optionally, registers content. Once the command has started, pressing the Enter key will execute the next instruction. As an example, enter the command **S R 0050:0100** and press the Enter key. This will execute the first instruction and terminate with registers content shown on the screen. When you press Enter again, the next instruction is executed. Continue pressing the Enter key until all instructions in the program get executed, or press the ESC key to terminate the command.

#### **1.5 Writing a Program Using Assembler on a PC**

In the pervious section, we have used the assemble command to write and load simple assembly instructions into the board memory. However, for more sophisticated applications, you need to write and assemble programs on a PC before downloading them into the board memory. For this purpose, you need the following programs:

- MASM: as the assembler and linker

- **EXE2BIN:** to convert from and executable file into a binary file

- **OBJECT86:** to convert the binary file into an INTEL HEX file for download to the FLIGHT-86

**Example 1.2:** Write a program to search for a given number in a list of numbers. You should define the list as a sequence of memory bytes labeled with the letter A. The number to be searched is passed through register DL. When the program terminate, BX should contain the index of the number in the list if the number is in the list.

COE305 LAB MANUAL

| ASSUME C | COMSEG SEGMENT BYTE PUBLIC 'CODE'<br>ASSUME CS:COMSEG, DS:COMSEG, ES:COMSEG, SS:COMSEG<br>ORG 0100h<br>start: |                                                                                                     |  |  |  |  |  |  |  |

|----------|---------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------|--|--|--|--|--|--|--|

| MC       | V AX,                                                                                                         | CS                                                                                                  |  |  |  |  |  |  |  |

| MC       | V DS,                                                                                                         | AX ; Set the data segment                                                                           |  |  |  |  |  |  |  |

| MC       | V BX,                                                                                                         | <pre>0 ; Set BX to index of the 1st element in ; the list</pre>                                     |  |  |  |  |  |  |  |

|          |                                                                                                               | 8 ; if BX exceeds the indices of the list                                                           |  |  |  |  |  |  |  |

| JZ       | L2                                                                                                            | ; then end the search                                                                               |  |  |  |  |  |  |  |

| JZ<br>IN | EP DL,<br>L2<br>C BX<br>EP L1                                                                                 | <pre>A[BX] ; if the number is found in the list   ; then end the search   ; else increment BX</pre> |  |  |  |  |  |  |  |

| L2: IN   |                                                                                                               | ; terminate the program                                                                             |  |  |  |  |  |  |  |

| A DE     | -                                                                                                             |                                                                                                     |  |  |  |  |  |  |  |

|          | 2                                                                                                             |                                                                                                     |  |  |  |  |  |  |  |

|          | 7                                                                                                             |                                                                                                     |  |  |  |  |  |  |  |

|          | 6                                                                                                             |                                                                                                     |  |  |  |  |  |  |  |

| DE       |                                                                                                               |                                                                                                     |  |  |  |  |  |  |  |

| DE       |                                                                                                               |                                                                                                     |  |  |  |  |  |  |  |

| DE       | 8                                                                                                             |                                                                                                     |  |  |  |  |  |  |  |

| COMSEG E | -                                                                                                             |                                                                                                     |  |  |  |  |  |  |  |

| END star | t                                                                                                             |                                                                                                     |  |  |  |  |  |  |  |

Using any text editor on the PC enter the previous code. Notice that the code shown in Bold is required for every program using **MASM** and can be thought of as a template. Now, save this file as **SEARCH.ASM**. Using the Assembler, i.e. MASM, assemble and link this file to produce **SEARCH.EXE**, and using **EXE2BIN** create the binary code file **SEARCH.BIN**. Now, using **OBJECT86**, convert this binary file to the Intel hex format file **SEARCH.HEX**. Finally load the HEX file into the board memory using the command ":**SEARCH.HEX**". Note, you may need to specify the drive and the path of the file if it is not in the same directory as the F86GO software (e.g. :C:\MyProjects\Search.hex).

To run this program, first load the required number into DX using the command **R DX**. Next, run the program using the command **G 0050:0100**. Finally, use the command **RX BX** to check result of the search (i.e. the value of BX represents the index of the given number in the list). These steps are shown below.

```

-R DX

DX 0000 0003

SP 0500

-G 0050:0100

User Break at 0050:011A

-R BX

BX 0004

-

```

#### **Exercises**

- **1.1.** Modify the program in **Example 1.1** to perform the four basic operations: *addition, subtraction, multiplication,* and *division.* The required operation is specified by loading DX with the appropriate value (i.e. 1 for addition, 2 for subtraction, 3 for multiplication, and 4 for division).

- **1.2.** Write a program to find the smallest number from a given list of numbers. Load this program into the FLIGTH-86 and test it.

# Conducting Simple I/O Operations Using Flight 86 Training Kit

#### Objective

The aim of this lab experiment is to conduct simple I/O operations, reading state of switches and turning on/off LEDs provided on the Application Board, by programming 8255 PPI chip.

#### Equipment

FLIGHT-86 training board, Application Board, PC with Flight86 software, download cable

#### Tasks to be Performed

- Interfacing the Application Board to the FLIGHT-86 training board.

- Conducting the following experiments

- 1. To read the state of a switch (on/off), and to output a signal to turn (on/off) an LED

- **2.** Generate a mod 16 counter and display the output on LEDs.

- **3.** Controlling the operation of the LEDs based on the state of a particular switch.

#### 2.1 Background

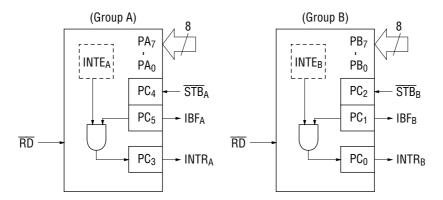

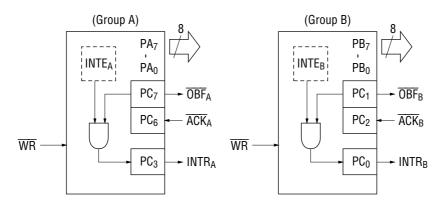

The FLIGHT-86 training board 'talks' to the Application Board by means of an Input/Output (I/O) device (i.e. 8255 PPI). This device is quite intelligent, and can perform input, output, and handshaking. However, before it will carry out any of these tasks, it must be told what is required of it. For I/O, it consists of three 8-bit ports. These ports can be set up as input or output ports.

Telling the PPI device how to perform is known as INITIALISATION. Thus, the first code we run after power up or reset, must be one which initializes the 8255. This little code will be required for every experiment.

In this experiment you will learn how to interface the Application Board to the FLIGHT-86 training board, program the 8255 PPI chip, and conduct simple I/O operations.

#### **2.2 The Application Board**

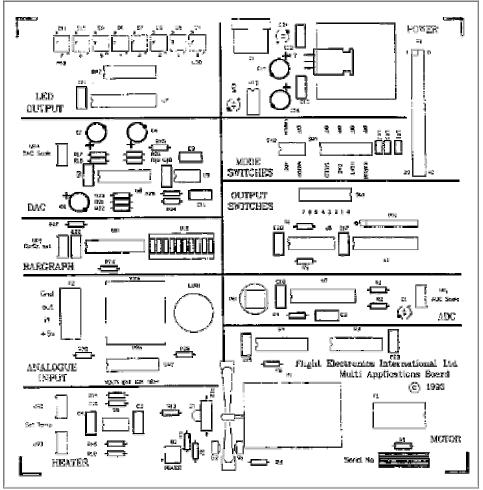

Figure 2.1 shows the layout of the Application Board that will be used to carryout a number of experiments. This board incorporates a wide array of electronic devices such as digital switches, LED displays, temperature, light, and optical position/speed sensors, a heater, a DC motor, an LED bar-graph, and a potentiometer. A screw terminal is also provided for external analog input.

The Application Board has two I/O ports (one for input and one for output) connected to a *parallel socket* (P1). The Processor output port connects to **Port-A** on the Application Board, and the state of the output port is always displayed on the 8-colored LEDs. This port can be used to control the motor (forward and reverse) and/or the heater. When not in use for these functions, the output port can be used to drive the Digital-to-Analog Converter (D/A). On the other hand, the processor input port connects to **Port-B** on the Application Board. This port can be used to read the 8-bit DIP switch, or the output of the Analog-to-Digital Converter (A/D), or the output of the D/A comparator, and/or the output of the speed sensing infrared detector.

The operation of the devices on the Application Board is controlled by means of the MODE SWITCHES. There are 6 mode switches divided into two groups (SW2 and SW4). Each switch enables/disables a certain device as shown in Table 2.1.

Figure 2.1: Layout of the Application Board

Table 2.1: Mode Switches

| Group | Switch | Operation                                                                    |

|-------|--------|------------------------------------------------------------------------------|

| SW2   | 1      | Enables either the 8-bit DIP switch or the Analog-to-Digital Converter (ADC) |

|       | 2      | Enables/disables the MOTOR                                                   |

|       | 1      | Enables/disables the speed sensor                                            |

| SW4   | 2      | Enables/disables the Digital-to-Analog Converter (DAC)                       |

| 577   | 3      | Enables/Disables                                                             |

|       | 4      | Enables/Disables the BARGRAPH                                                |

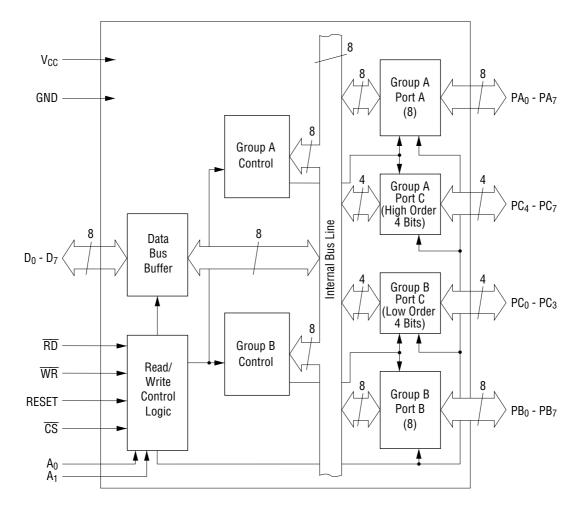

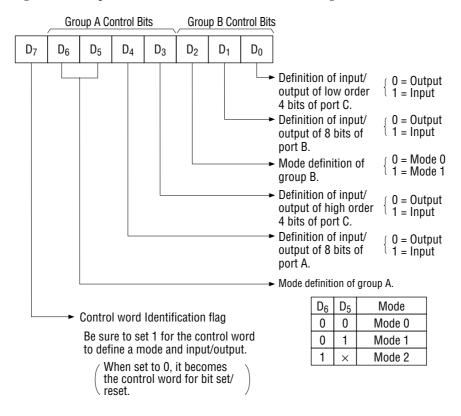

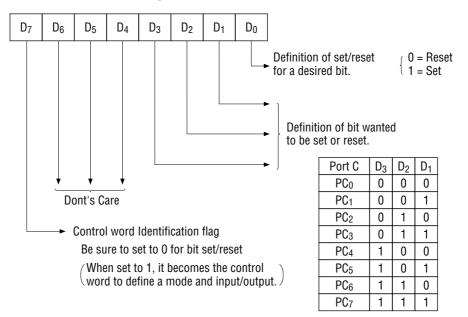

#### 2.3 Programming the 8255 PPI Chip

The 8255 is a general-purpose parallel I/O interfacing device. It provides 24 I/O lines organized as three 8-bit I/O ports labeled A, B, and C. In addition to these three ports, a third port (Control) is used to program the chip. Each of the ports, A or B, can be programmed as an 8-bit input or output port. Port C can be divided in half, with the topmost or bottommost four bits programmed as inputs or outputs. Individual bits of a particular port cannot be programmed. In the FLIGTH-86 training board, the 8255 PPI chip is interfaced to two parallel port sockets P1 and P2. In each socket, each one the four ports (A, B, C, and Control) has an individual address as shown in Table 2.2.

| D   | Port  | Activity allowed | Actual port address |    |  |  |

|-----|-------|------------------|---------------------|----|--|--|

| ſ   |       | Activity allowed | P1                  | P2 |  |  |

| Por | tΑ    | Read/Write       | 00                  | 01 |  |  |

| Por | t B   | Read/Write       | 02                  | 03 |  |  |

| Por | t C   | Read/Write       | 04                  | 05 |  |  |

| Co  | ntrol | Write only       | 06                  | 07 |  |  |

Table 2.2: 8255 port addresses

The 8255 PPI chip can be programmed to operate in three modes:

- Mode 0 Basic Input/Output

- Mode 1 Strobed Input/Output

- Mode 2 Bi-directional bus (not available on FLIGHT-86)

There is also a *bit set/reset mode* that allows individual bits of port C to be set or reset for control purposes.

In this experiment, you will learn how to initialize the 8255 PPI chip to operate in Mode 0. To learn about programming the 8255 PPI chip in other modes you can refer to your text book.

Mode 0 gives the simplest form of I/O possible, where no 'handshaking' is required. Data is simply read from or written to the specified port. Any one of the ports A, B, C (upper half), and C (lower half) can be set individually as input or output ports. This is done by sending a control byte to the Control Port. The 16 possible control words are shown in Table 2.3. Notice that D7, D6, D5, and D2 are fixed for this mode. For example, to set the three ports as output ports, you need to send the control word 80h to the Control port using the following set of instructions:

```

MOV AL, 80H ; load AL with the control word 80H

OUT 06H, AL ; send this control word to port 60H

; (i.e. the Control port)

```

| Ports |            |     | Control Word |    |    |    |    |    |    |    |    |

|-------|------------|-----|--------------|----|----|----|----|----|----|----|----|

| Α     | C (higher) | В   | C (lower)    | D7 | D6 | D5 | D4 | D3 | D2 | D1 | DO |

| OUT   | OUT        | OUT | OUT          | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 0  |

| OUT   | OUT        | OUT | IN           | 1  | 0  | 0  | 0  | 0  | 0  | 0  | 1  |

| OUT   | OUT        | IN  | OUT          | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 0  |

| OUT   | OUT        | IN  | IN           | 1  | 0  | 0  | 0  | 0  | 0  | 1  | 1  |

| OUT   | IN         | OUT | OUT          | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 0  |

| OUT   | IN         | OUT | IN           | 1  | 0  | 0  | 0  | 1  | 0  | 0  | 1  |

| OUT   | IN         | IN  | OUT          | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 0  |

| OUT   | IN         | IN  | IN           | 1  | 0  | 0  | 0  | 1  | 0  | 1  | 1  |

| IN    | OUT        | OUT | OUT          | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 0  |

| IN    | OUT        | OUT | IN           | 1  | 0  | 0  | 1  | 0  | 0  | 0  | 1  |

| IN    | OUT        | IN  | OUT          | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 0  |

| IN    | OUT        | IN  | IN           | 1  | 0  | 0  | 1  | 0  | 0  | 1  | 1  |

| IN    | IN         | OUT | OUT          | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 0  |

| IN    | IN         | OUT | IN           | 1  | 0  | 0  | 1  | 1  | 0  | 0  | 1  |

| IN    | IN         | IN  | OUT          | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 0  |

| IN    | IN         | IN  | IN           | 1  | 0  | 0  | 1  | 1  | 0  | 1  | 1  |

Table 2.3: Control words for Mode 0

### 2.4 Conducting Simple Experiments Using the Application Board

In this section, you will learn how to write simple programs to read the states of the switches and turn on/off the LEDs on the Application Board connected to the FLIGHT-86 training board. These programs will be assembled on the PC, and then downloaded to the training board. In this way, you can keep your programs on the PC, and easily modify them or link them with other programs.

**Example 2.1:** Write a program to read the state of a switch (on/off) and display it on the corresponding LED.

| 1  | COMSEG SEGMENT BYTE PUBLIC 'CODE'                    |

|----|------------------------------------------------------|

| 2  | ASSUME CS:COMSEG, DS:COMSEG, ES:COMSEG, SS:COMSEG    |

| 3  | ORG 0100h                                            |

| 4  | start:                                               |

| 5  | MOV AL, 99h; Port A IN, Port B OUT, Port C OUT       |

| 6  | OUT 06h, AL; output control word to the Control Port |

| 7  | L1: IN AL, 00h; read the states of the switches      |

| 8  | OUT 02h, AL; display the output on the LEDs          |

| 9  | JMP L1                                               |

| 10 | COMSEG ENDS                                          |

| 11 | END start                                            |

Lines 4 and 5 in the above code initialize the 8255 PPI chip in Mode 0, such that ports A and C are set as input ports while port B is set as an output port. Then, the program enters a continuous loop that reads the states of the switches into AL and displays them on the LEDs. Reading the states of the switches (line 7) is done through port A (00h), while displaying the output on the LEDs (line 8) is done through port B (02h).

**Example 2.2:** Write a program to generate modulo 16 counter and display the output on the LEDs.

```

COMSEG SEGMENT BYTE PUBLIC 'CODE'

1

2

ASSUME CS:COMSEG, DS:COMSEG, ES:COMSEG, SS:COMSEG

3

ORG 0100h

4

start:

5

MOV BL, 16

MOV AL, 99h

; Port A IN, Port B OUT, Port C OUT

6

OUT 06h, AL

7

; output control word to the Control Port

8

MOV AX, 0

; initialize the counter to 0

9

L1: OUT 02h, AL

; display the counter on the LEDs

MOV CX, OFFFh ; delay loop

10

11 L2: LOOP L2

; increment the counter

12

INC AL

DIV BL

; AH = AL mod 16

13

MOV AL, AH

14

15

MOV AH, 0

16

JMP L1

17 COMSEG ENDS

18 END start

```

The previous code starts as usual by initializing the 8255 PPI chip (lines 6 and 7). The counter is initialized in line 8. Line 9 displays the counter on the LEDs through port B (02h). Then, the program enters a delay loop (lines 10 to 12) before incrementing the counter in line 13. Since a module 16 counting is required, the counter (i.e. AX) is divided by 16 and the remainder is loaded back into AX (lines 14 to 16). Notice that instruction in line 14 divides AX by 16, leaving the quotient in AL and the remainder in AH.

### **Exercises**

**2.1.** Write a program to generate the following based on the state of a particular switch

| Switch 1:  | ON  | Generate a mod 8 counter and display it on LEDs                                                                                                                                                                                                                     |  |

|------------|-----|---------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|--|

|            | OFF | Switch off all LEDs                                                                                                                                                                                                                                                 |  |

| Switch 2 : | ON  | Generate a mod 256 counter and display it on LEDs                                                                                                                                                                                                                   |  |

|            | OFF | Switch off all LEDs                                                                                                                                                                                                                                                 |  |

| Switch 3 : | ON  | Light LEDs one after another one at a time in a sequence from left to right (from first LED to Last LED). When one LED is on, all other LEDs must be switched off. ( i.e., shifting bit '1' from left to right). Repeat this cycle until the switch 3 is turned OFF |  |

| Switch 4 : | ON  | Repeat the above from last LED to the first                                                                                                                                                                                                                         |  |

**2.2.** Write a program to add 2 four-bit numbers and display the result on the LEDs. The two numbers are entered through the 8-DIP switch provided on the Application Board (i.e. each 4 switches represent one number).

# Experiment

### Generating Timing Sequences

### Objective

The aim of this lab experiment is to generate timing sequences using software delays and programming 8253 Programmable Interval Timer (PIT) chip.

### Equipment

Flight 8086 training board, the Application Board, PC with Flight86 software, download cable

### **Tasks to be Performed**

- Generate time delays using software delays and 8253 PIT chip.

- Use generated delays to turn ON/OFF LEDs for specific amounts of time

- Generate waveforms of different frequencies, and observe them on an oscilloscope/logic analyzer.

- Interface a simple relay driver circuit to 8255 port and switch ON/OFF a device for a specific amount of time.

### 3.1 Background

It is often necessary to control how long certain actions last. This can be achieved using software delays, or more accurately by the use of a timer (i.e. 8253 PIT chip). In this experiment, you will learn how to generate time delays using both software delays and 8253 PIT chip. Also, you will learn how to use time delays to control the operation of some devices (e.g. LEDs and Relays), and to generate periodical waveforms of different frequencies.

### 3.2 Software Delays

The easiest way to generate delays is a software delay. If we create a program which loops around itself, and does this for a fixed number of times, for a given processor, running at a given clock rate, this process will almost take the same time each time the program is executed. All we have to do is to write this loop such that it takes 1 second. Then, by calling this loop *n* times, we generate a delay of *n* seconds. Notice that the time taken by the loop does not need to be 1 second. For example, a loop that takes 0.25 seconds to execute, can be called  $4 \times n$  times (i.e. n/0.25) to generate a delay of *n* seconds. The question now is **how to determine the time taken by a loop**. This can be answered by the following example.

Example 3.1: Calculate the total time taken by the following loop.

```

MOV CX, 8000h; load CX with a fixed value 8000h (32768)

L1: DEC CX ; decrement CX, loop if not zero

JNZ L1

```

From the 8086 data sheets, we find that **DEC CX** requires 2 clock cycles and **JNZ** requires 16 clock cycles. Thus, the total number of clock cycles required by these two instructions is **18** clock cycles.

Since the FLIGHT-86 board is running at 14.7456/3 MHz, 1 clock cycle will take 3/14.7456 microseconds, and 18 clock cycles will take 54/14.7456 microseconds. Thus, the total time taken by the loop is  $32768 \times (54/14.7456 \times 10^{-6}) = 0.12$  seconds

The previous loop requires 0.12 seconds. Thus, this loop needs to be executed almost 8 times to generate a delay of 1 second. The following example shows how to use this loop inside a program to turn ON/OFF an LED for specific amounts of time.

**Example 3.2:** Write a program to turn ON an LED for 3 seconds, then turn it OFF for another 3 seconds, and repeat this cycle.

```

COMSEG SEGMENT BYTE PUBLIC 'CODE'

ASSUME CS:COMSEG, DS:COMSEG, ES:COMSEG, SS:COMSEG

ORG 0100h

Start:

MOV

AL, 99h ; initialize 8255 ports:

OUT

06h, AL ; A and C in, B out

AL, 01h ; set bit 0 in AL to 1

MOV

02h, AL ; turn on/off LED 0

ON OFF:

OUT

DL, 25 ; delay of 25*0.12 = 3 sec

MOV

Delay

CALL

AL, 01h ; complement bit 0 in AL

XOR

JMP

ON OFF

Delay

PROC

L1:

CX, 8000h

MOV

L2:

DEC

CX

JNZ

L2

DEC

DT.

JNZ

L1

RET

Delay

ENDP

COMSEG

ENDS

END Start

```

Run the above program on the FLIGHT-86 board and estimate the ON/OFF time of LED 0. What you conclude about the accuracy of the software delays?

### 3.3 Time Delays Using the 8253 PIT Chip

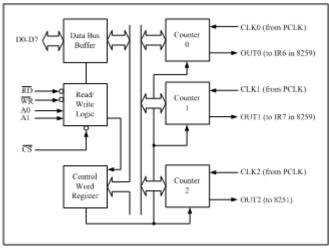

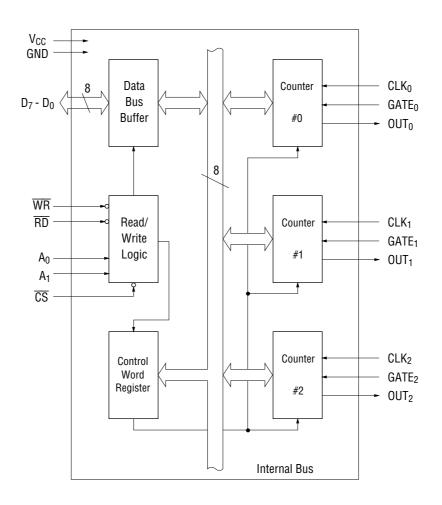

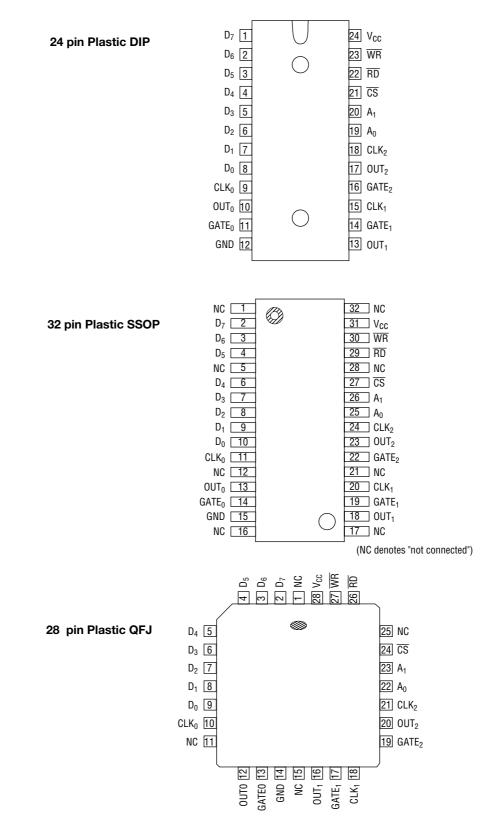

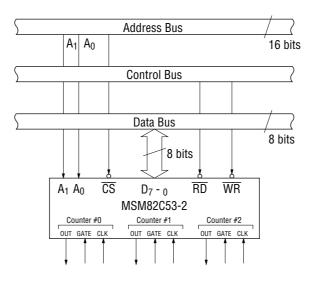

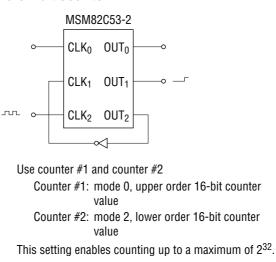

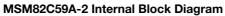

Software delays are the easiest way to generate time-delays, as they do not require any additional hardware. However, software delays are not accurate especially for long delays. Therefore, timers like the 8253 PIT chip are used to generate accurate delays. Figure 3.1 shows the circuit diagram of the 8253 PIT chip. It consists mainly of three identical counters (Counter0 to Counter2) and one Control Word Register.

### **Counting and Control Registers of the 8253 PIC Chip**

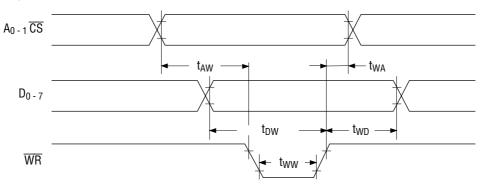

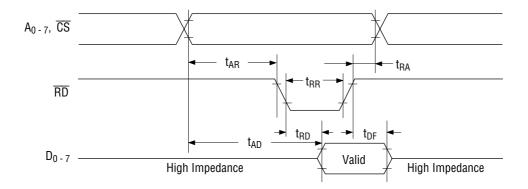

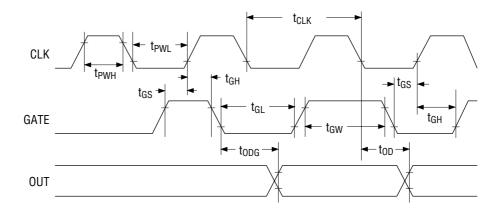

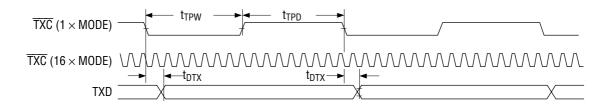

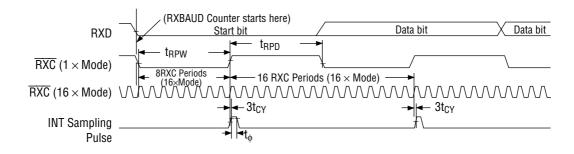

The three counters are 16-bit *count down* registers, which decrement on the falling edge of their input clocks (CLK0 to CLK2). In the case of the FLIGHT-86, CLK0 to CLK2 are connected to the PCLK clock that is running at **14.7456/6** MHz. Thus, the counters will be decremented every **6/14.7456** microseconds. The three counters are loaded through the low byte of the data bus (D0-D7). Hence, two write cycles are required to load any one of the 16-bit registers. The Control Word register is used to determine the mode, size and type of count for each counter to be used.

Figure 3.1: The 8253 PIT circuit diagram

Each one of the previous registers has a unique address, and can be accessed using I/O operations (i.e. IN and OUT). Table 3.1, shows the addresses assigned to four registers in the FLIGHT-86 board.

| Register     | Activity Allowed | Actual Port Address |

|--------------|------------------|---------------------|

| Counter 0    | Read/Write       | 08h                 |

| Counter 1    | Read/Write       | 0Ah                 |

| Counter 2    | Read/Write       | 0Ch                 |

| Control Word | Write Only       | 0Eh                 |

Table 3.1: The 8253 PIT chip register addresses

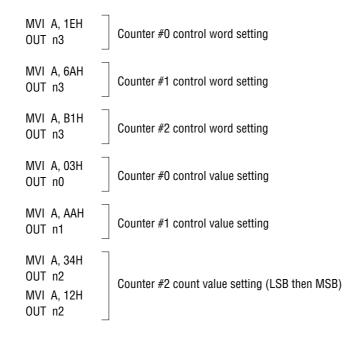

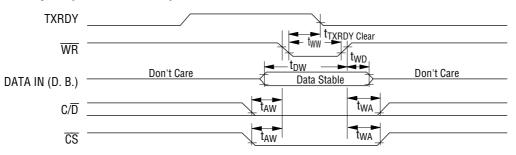

### **Programming the 8253 PIT Chip**

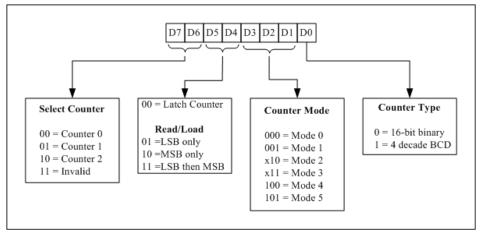

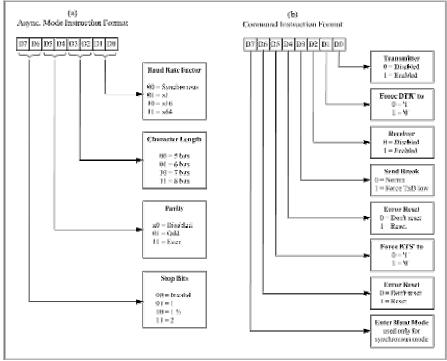

Each counter of the 8253 PIT chip can be programmed independent from the other counter by sending a control word to the Control Word Register. Figure 3.2 shows the format of the control word. Bit D0 specifies counting type (i.e. binary or BDC). Bits D3, D2, and D1 specify the counting mode. Bits D5 and D4 specify how the counter is read and loaded. Bits D7 and D6 specify the counter to be programmed (i.e. Counter 0 to Counter 2).

There are four options for reading/loading the counter:

- **1.** Latch Counter: allows you to latch the current register count, and then read the counter value 'on the fly'

- **2.** Read/Load Least Significant Byte (LSB): only the low byte of the counter can be read or loaded

- **3.** Read/Load Most Significant Byte (MSB): only the high byte of the counter can be read or loaded

- **4.** Read/Load Least LSB then MSB: allows two bytes to be read from or loaded into the counter such that the LSB comes first.

Figure 3.2: Control Word Format of the 8253 PIT Chip

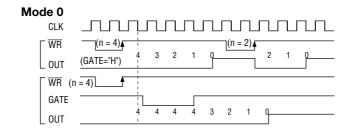

As indicated in Figure 3.2, there are six counting modes:

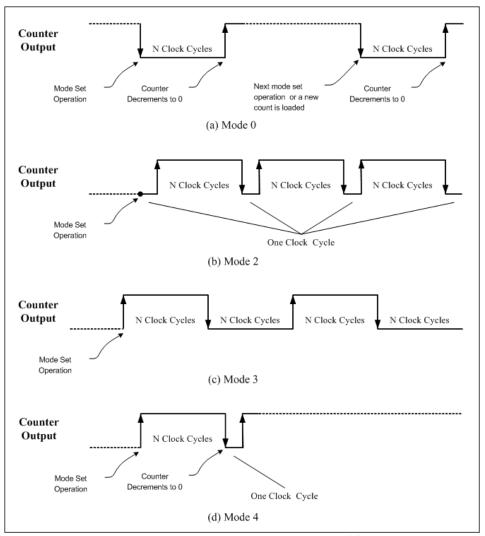

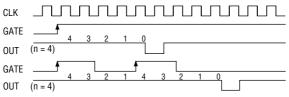

**Mode 0 - Interrupt on Terminal Count:** The output goes low after the mode set operation, and remains low while counting down. When the count decrements to zero, the output goes high and remains high until then next mode is set or a new count is loaded. See Figure 3.3 (a).

Mode 1 - Programmable One-shot: not available on FLIGHT-86

**Mode 2 - Rate Generator:** A divide by N counter. The output is low for one input clock period and then high for N clock periods. This cycle repeats until a new mode is selected. See Figure 3.3 (b).

**Mode 3 - Square Wave Rate Generator:** Similar to Mode 2, except that the output is high for the first half of the count and goes low for the other half. See Figure 3.3 (c).

**Mode 4 - Software Triggered Strobe:** The output goes high once the mode is set, and remains high while the counter is decremented. When the counter decrements to zero, the output goes low for one clock cycle and then goes high again. The output will remain high until a new mode or count is loaded. See Figure 3.3 (d).

Mode 5 -Hardware Triggered Strobe: not available on FLIGHT-86.

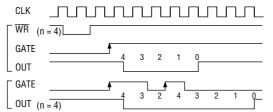

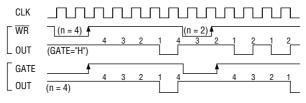

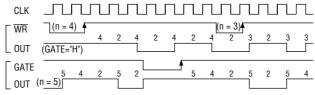

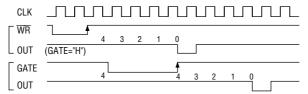

Figure 3.3: Counting modes of the 8253 PIT chip

In order to program any one of the three counters in a certain mode, you need to do two things. First, send a control word to the Control Word Register. Then, load a proper value into the counter register. These two steps are illustrated in the following example.

Example 3.3: Write an assembly code to do the following:(1) Set Counter0 as a 16-bit binary counter operating in Mode0(2) Load Counter0 with the proper value, such that OUT0 goes high after 0.025 seconds.

(1) The required control word is shown below:

```

0 0 1 1 0 0 0 0 = 30h

| | | |16 bit binary counter

| | Mode 0

| Read/Load LSB then MSB

|Counter 0

```

(2) Since the counter clock input is connected to PCLK (14.7456/6 MHz), it will be decremented every 6/14.7456 microseconds. Hence, we need to load the counter with the value (0.025 × 14.7456 × 10<sup>-6</sup>)/6 = 61440 = F000h.

The following code will load the required control word (i.e. 30h) into the Control Word Register, and will load Counter0 with F000h.

MOV AL, 30h ; load the control word into AL OUT OEh, AL ; and send it to the Control Register ; since the 8253 PIT chip is connected to the low byte of ; the data bus, two write cycles are required to load ; F000h into counter0 MOV AL, 00h ; load the low byte of F000h OUT 08h, AL ; into low byte of Counter0 MOV AL, F0h ; load the high byte of F000h OUT 08h, AL ; into high byte of Counter0

### Handling the Outputs of Counter0 and Counter1

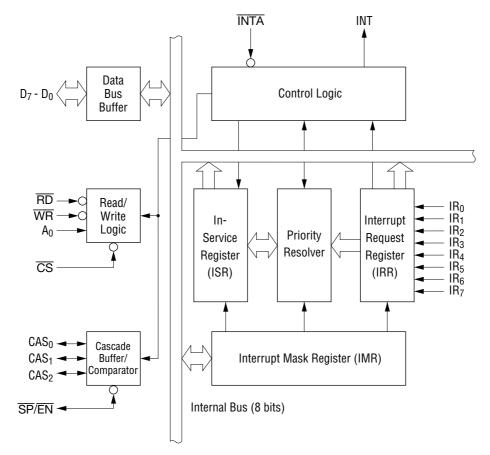

You may noticed that the outputs of Counter0 and Counter1 (i.e. OUT0 and OUT1) in Figure 3.1 are connected to inputs IR6 and IR7 of the 8259 chip respectively. This allows these two counters to operate in an interrupt driven manner. The 8259 Programmable Interrupt Control (PIC) chip accepts requests from the peripheral chips through inputs IR0 to IR7, and determines which of the incoming requests has the highest priority. Then, it issues the interrupt to the 8086 processor together with the

*interrupt pointer* to enable the correct Interrupt Service Routine (ISR) to be executed. The 8259 PIC chip can be programmed to perform a number of modes of operation, which may be changed dynamically at any time in the program. Programming the 8253 PIC chip is not covered in this experiment. Instead, you will be given the necessary code to set the chip in a proper mode of operation.

When the output of Counter0/Counter1 goes high, it generates a request on IR6/IR7. The 8253 PIC chip handles this request as follows. If maskable interrupts are enabled by the instruction **STI**, the 8259 will send an interrupt to the 8086 via the **INT** line. The 8086 acknowledges the interrupt request with an INTA pulse. Upon receipt of the INTA from the 8086, the 8259 freezes the pending interrupts and waits for another INTA pulse. When the 8086 sends the second INTA, the 8259 treats this as a Read pulse and places an 8-bit pointer onto the data bus. The pointers corresponding to requests on IR6 and IR7 are 38 and 39 respectively.

The 8086 processor uses the 8-bit pointer to fetch the address (i.e. *offset* and *segment*) of the corresponding ISR from the **Interrupt Vector Table (IVT)**. This is done as follows. Suppose that the 8-bit pointer is *n*, then the 8086 will fetch **four bytes** starting from the address **0000**:*n*\*4. The first two bytes contain the offset of the ISR, while the next two bytes contain the segment of the ISR.

### **Illustrative Example**

The following example illustrates how to program the 8253 PIT and 8259 PIC chips to generate time delays.

**Example 3.4:** Write a program to turn ON an LED for 3 seconds, then turn it OFF for another 3 seconds, and repeats this cycle. Do not use software delays.

| 1              | COMSEG SEGMENT BYTE PUBLIC 'CODE'                                                |

|----------------|----------------------------------------------------------------------------------|

| 2              | ASSUME CS:COMSEG, DS:COMSEG, ES:COMSEG, SS:COMSEG                                |

| 3              | ORG 0100h                                                                        |

| 4              | Start: ; set the extra segment to point to the                                   |

| 5              | ; base of the Interrupt Vector Table (IVR)                                       |

| 6              | XOR AX,AX                                                                        |

| 7              | MOV ES,AX                                                                        |

| 8<br>9<br>10   | ;store the offset of ISR in the IVT<br>MOV WORD PTR ES:[38*4],OFFSET IR6_ROUTINE |

| 11<br>12<br>13 | ;store the segment of ISR in the IVT<br>MOV WORD PTR ES:[38*4+2],CS              |

| 14             | ; initialize the 8255 PPI chip:                                                  |

| 15             | ; A and C input ports, B output port                                             |

| 16             | MOV AL, 99h                                                                      |

| 17             | OUT 06h, AL                                                                      |

### COE305 LAB MANUAL 18 ; initialize the 8259 PIC chip 19 MOV AL, 17h OUT 10h, AL 20 21 MOV AL, 20h 22 OUT 12h, AL 23 MOV AL, 03h 24 OUT 12h, AL MOV AL, 3Fh 25 OUT 12h, AL 26 27 ; initialize 8253 PIT chip (00110110 = 36h) ; Counter0, load MSB then LSB, mode 3, binary 28 29 MOV AL, 36h 30 OUT OEh, AL 31 ; counter loaded with F000h for 25 ms delay 32 MOV AL, 00h OUT 08h, AL ; first load low byte 33 34 MOV AL, OFOh 35 OUT 08h, AL ; now load high byte 36 ; enable 8086 maskable interrupts STI 37 MOV DL, 120 ; count for 120 interrupts (3s) 38 ; start of main program 39 ; switch off all LEDs MOV DH, 00h 40 41 MOV AL, DH 42 OUT 02h, AL 43 Again: JMP Again ; wait for interrupt on IR6 44 ; (Counter0 decrements to 0) 45 ; Interrupt Service Routine (ISR) for IR6 46 ; this routine toggles ON/OFF LED 0 every 3 seconds 47 IR6 ROUTINE: 48 DEC DL ; decrement interrupts counter CMP DL,0 ; if counter < 120 JNZ Return ; then exit ISR 49 50 51 XOR DH, 01h ; else toggle LED0 52 MOV AL, DH 53 OUT 02h, AL 54 MOV DL, 120 ; count for 120 interrupts (3s) 55 Return: IRET 56 COMSEG ENDS 57 END start

In the previous program, lines 6 and 7 set the ES segment to 0000h, which is the base address of the IVT. Lines 9 and 12 load the starting address of the ISR (IR6\_ROUTINE) into the IVT. This routine will handle any request on IR6. Lines 16 and 17 initialize the 8255 PPI chip. Lines 19 to 26 initialize the 8259 PIC chip. Lines 29 and 20 initialize the 8253 PIT chip. Lines 32 to 35 load the Counter0 with the value F000h. This will generate an interrupt every 25 ms (120 interrupts every 3 seconds). The main routine starts by setting all LEDs off by sending 00h to port B (Lines 40 to 42), and waits for an interrupt on IR6 (Line 43). Upon receipt of the interrupt, the control is transferred to IR6\_ROUTINE (Line 47). This routine toggles LED0 every 120 interrupts (i.e. every 3 seconds).

### **Exercises**

**3.1.** Consider the following loop:

What value of Y makes the loop executes in 0.225 seconds?

- **3.2.** Modify the program in Example 3.2 such that Counter0 is set in Mode 0

- **3.3.** Generate square waveforms with the following frequencies:

- a. 100 KHz

- b. 10 KHz

- c. 1 KHz

- **3.4.** Interface a simple relay driver circuit to 8255 port, and write a program switch ON/OFF a lamp every 10 seconds.

- **3.5.** Write a program to simulate a traffic light controller (home assignment)

- **3.6.** Write a program to simulate a lift controller (home assignment)

# Experiment

### Analog to Digital & Digital to Analog Conversion

### Objective

The aim of this lab experiment is to study the Analog to Digital conversion and Digital to Analog conversion.

### Equipment

Flight 8086 training board, Application board, PC with Flight86 software, download cable.

### **Tasks to be Performed**

- Simulation of a A/D conversion employing successive approximation method using D/A converter

- Use a D/A converter to perform the following:

- **1.** Sine wave generation (using look up table)

- 2. Staircase waveform generation

- **3.** Saw-tooth waveform generation

- Read the DIL switches and output the digital values to the LEDs and DAC. The analog output of the DAC is to be represented by lighting up the bargraph.

### 4.1 Background

In any computer controlled process it may be required to monitor analog values, i.e. the output of a voltmeter or strain gauge. In order to do this, the analog signal must be first converted into a digital value using an Analog-to-Digital Converter (A/D). On the other hand, Digital-to-Analog Converters (D/A) can be used to convert a digital output from the computer into an analog value. For instance, we could generate a series of tones by changing the digital output values in such a way that the analog signal is represented as a sine wave.

### 4.2 A/D Conversion

The Application Board provides four sources of analog inputs which can be selected using a four position switch (SW3). The analog source can be provided externally (P2-in), or from the output of a light dependent resistor (LDR1), or from the temperature sensor (Q1), or from an on board variable voltage (UR6).

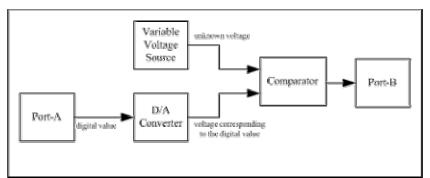

With the Application Board we can simulate a simple A/D converter that reads the output of a certain analog source (e.g. variable voltage) and converts it into a digital value as shown in Figure 4.1. By means sending values to Port-B, and hence by means of the D/A converter we can generate analog voltages proportional to the digital value we output. If this analog voltage is now compared with the unknown analog voltage, we can gradually adjust the output value to Port-A, until the comparator finds the two analog voltages equal. The digital value output to the D/A converter must be the digital value equivalent of the unknown analog input.

The output of the comparator is bit 3 of the input Port-B. A logic 1 means the output on Port-B is too small, a logic 0 means it is too large.

Figure 4.1: Simulation of an A/D Converter

**Example 4.1:** Write a program to simulate a simple A/D converter. Use the variable voltage source (UR6) as your analog source. The program should display one HEX digit (0-F) representing the digital value of the voltage input.

|             | Set SW3 to VOLTS (Variable Voltage)<br>Set SW4-2 to DAC (enable D/A converter)<br>Set SW2-2, SW4-1, SW4-3, and SW4-4 OFF |

|-------------|--------------------------------------------------------------------------------------------------------------------------|

| 1           | COMSEG SEGMENT BYTE PUBLIC 'CODE'                                                                                        |

| 2           | ASSUME CS:COMSEG, DS:COMSEG, ES:COMSEG, SS:COMSEG                                                                        |

| 3           | ORG 0100h                                                                                                                |

| 4           | Start:                                                                                                                   |

| 5           | MOV AL, 99h ; initialize the 8255 PPI chip                                                                               |

| 6           | OUT 06h, AL ; A input, B output, C input                                                                                 |

| 7<br>8<br>9 | MOV AL, 0 ; turn off all LEDs<br>OUT 02h, AL                                                                             |

| 10          | ANAL: MOV BL, 0 ; first digital value                                                                                    |

| 11          | SMALL: MOV AL, BL ; put in AL for output                                                                                 |

| 12          | OUT 02h, AL ; output value to D/A                                                                                        |

| 13          | NOP ; wait for D/A                                                                                                       |

| 14          | NOP                                                                                                                      |

| 15          | NOP                                                                                                                      |

| 16          | NOP                                                                                                                      |

| 17          | NOP                                                                                                                      |

| 18          | NOP                                                                                                                      |

| 19          | IN AL, OOh ; get input Port-B                                                                                            |

| 20          | AND AL, O8h ; keep comparator bit (bit 3)                                                                                |

| 21          | JZ LARGE ; if value is large (bit3= 0)                                                                                   |

| 22          | ; then display the digital value                                                                                         |

| 23          | INC BL ; else increment the digital value                                                                                |

| 24          | JMP SMALL ; and tray again                                                                                               |

| 25          | ; display the digital value as a HEX digit                                                                               |

| 26          | LARGE: MOV AL, BL                                                                                                        |